パルスジェネレータは、設計とセットアップのラボの研究に使用されます 電子デバイス。 発電機は、7〜41ボルトの電圧範囲で動作し、出力トランジスタに応じて高負荷容量で動作します。 出力パルスの振幅は、マイクロ回路の電源電圧の値に等しいことができ、このマイクロ回路の電源電圧の限界値までは+ 41Vである。

類似体 TL494 マイクロ回路 KA7500 国内のクローン - КР1114ЕУ4 .

パラメータの値を制限する:

電源41V

アンプの入力電圧(Vcc + 0.3)V

コレクタ出力電圧41V

コレクタ出力電流250mA

連続モードでの合計消費電力1W

動作温度範囲:

接尾辞L-25..85Сの付いた-c

接尾辞付きС.0..70С

保管温度範囲-65 ... +150С

デバイスの概略図

矩形パルス発生器の構成

ジェネレータプリント基板 TL494 他のファイルは別のフォルダにあります。

周波数調整はスイッチS2(粗)と抵抗RV1(スムーズ)により実行され、デューティサイクルは抵抗RV2によって調整されます。 スイッチSA1は、発電機の動作モードを同相(単一サイクル)から逆相(2サイクル)に変更する。 抵抗R3は最適なオーバーラップ周波数範囲を選択し、デューティサイクルの調整範囲は抵抗R1、R2によって選択することができます。

パルスジェネレータの詳細

時間のかかる回路のコンデンサC1~C4は、要求される周波数範囲に対して選択され、それらの容量は、最も低い周波数のサブバンドから1000μFの周波数まで、10マイクロファラドから可能である。

平均電流が200mAに制限されている場合、回路はシャッターを急速に充電することができますが、

トランジスタをオフにして放電することは不可能です。 シャッターを接地された抵抗器で放電してください。 これらの目的のために、独立した相補リピータが使用されます。

- 「コンピュータからの作り方」を読んでください。

PULSE POWER SUPPLY UNITの電源キーの管理

AID TL494

この記事は、AV GolovkovaとVB Lyubitsky出版社「LADとH」「タイプIBM PC-XT / ATのシステムモジュールのPSU」の著書に基づいて調製しました

コントローラMICROCIRCUIT TL494

制御スイッチング電圧を形成するための現代のUPS 強力なトランジスタ コンバータは通常特殊集積回路(IC)を使用します。

PWMモードでのUPSの適切な動作のための理想的な制御ICは、以下の条件のほとんどを満たす必要があります。

動作電圧 40V以下であること。

非常に安定した熱安定化された基準電圧源の存在;

鋸歯状電圧発生器の存在

プログラム可能なソフトスタートの外部信号との同期の可能性。

コモンモード電圧が高いミスマッチ信号増幅器が存在する。

PWMコンパレータの存在。

パルス制御されたトリガーの存在;

短絡からの保護を備えた2チャンネルのプレ有限カスケードの存在。

ダブルパルス抑制論理の存在;

出力電圧の対称性を補正する手段の利用可能性;

広範囲のコモンモード電圧における電流制限の存在、および緊急モードで切断された各期間の電流制限、

直接送信による自動制御の存在;

電源電圧が低下したときにシャットダウンを行う。

過電圧に対する保護。

TTL / CMOSロジックとの互換性。

リモートオンとオフを提供します。

図11制御IC TL494とそのピン配列。

検討されている種類のスイッチング電源の制御回路としては、TEXAS INSTRUMENT(米国)製のチップタイプTL494CNを使用しています(図11)。 上記の機能のほとんどを実現し、異なる名前で多数の外国企業によって発行されます。 たとえば、会社シャープ(日本)チップIR3M02を生成し、しっかりフェアチャイルド(US) - UA494、しっかりSAMSUNG(韓国) - KA7500、しっかり富士通(日本) - MV3759など これらのチップはすべて国内のチップKR1114EU4の完全アナログです。 この制御用マイクロ回路のデバイスと動作を詳細に検討しましょう。 これは、UPSの電源部分を制御するために特別に設計され、その構成に含まれています(図12):

図12. TL494の機能図

発電機ノコギリ波電圧DA6; GPNの周波数は、第5および第6の端子に接続された抵抗およびコンデンサの値によって決定され、考慮されるクラスでは、BPは約60kHzに選択される。

外部出力(ピン14)での基準安定化電圧源DA5(Uref = + 5、OB)。

「デッドゾーン」コンパレータDA1。

PWM DA2コンパレータ。

電圧誤差増幅器DA3;

電流制限信号DA4に応じた誤差増幅器と、

オープンコレクタおよびエミッタを有する2つの出力トランジスタVT1およびVT2と、

周波数を2-DD2で除算するモードのダイナミック2ストロークD-フリップフロップ、

補助論理要素DD1(2-OR)、DD3(2-D)、DD4(2-D)、DD5(2-OR-NONE)、DD6(2-OR-NOT)、DD7(HE)

定格0.1BDA7の定電圧源。

ソース 直流 0.7mA DA8の公称値である。

制御スキームが開始される。 端末12は+7と40 V. IC TL494に含まれる機能ユニットのセット全体との間でレベルが任意の電圧源を適用する場合は8と11の所見は、パルスの系列で表示され、デジタルに分けることができます。 アナログ部(デジタルとアナログの信号経路)があります。 アナログ部は、誤差増幅器DA3、DA4、比較器DA1、DA2、鋸歯状波電圧DA6の発生器、および補助電源DA5、DA7、DA8を含む。 出力トランジスタを含む他のすべての要素は、デジタル部分(デジタル経路)を形成する。

図13. TL494 IMSの操作 公称モード:U3、U4、U5 - 端子3,4,5の電圧。

最初にデジタル経路の作業を検討してください。 チップの動作を説明するタイミング図を図5に示す。 制御回路の出力パルスの発生、ならびにそれらの長さのモーメント(12及び13図)ことが明らかである時間図から13は、NANDゲートDD1の出力状態(図5)によって決定されます。 残りの「論理」は、出力パルスDD1を2つのチャネルに分割する補助機能のみを実行する。 この場合、マイクロ回路の出力パルスの持続時間は、その出力トランジスタVT1、VT2の開放状態の持続時間によって決定される。 これらのトランジスタは両方ともオープンコレクタとエミッタを有するので、それらが2つの方法で接続されている可能性がある。 共通エミッタによってイネーブルされたとき、出力パルスが(ピン8と11個のチップの)外部コレクタ負荷トランジスタから取り出し、それ自体のパルス放出は正のレベルから下方に向けられる(パルスの前縁は負です)。 この場合、トランジスタのエミッタ(チップの9,10番端子)は、一般に接地されている。 、共通コレクタ外部負荷トランジスタの出力パルスのエミッタに接続されており、この場合には向け、放射上方(パルスの正の立ち上がりエッジ)をオンにすると、トランジスタVT1、VT2のエミッタから除去されます。 これらのトランジスタのコレクタは、制御チップ(Upom)の電源バスに接続されている。

TL494のデジタル部分の一部である残りの機能ノードの出力パルスは、マイクロサーキットの回路に関係なく、上方に向いています。

トリガDD2は、2ストロークダイナミックDフリップフロップです。 彼の仕事の原則は次の通りです。 DD1素子の出力パルスの正(正)エッジでは、DD2トリガのD入力の状態が内部レジスタに書き込まれます。 物理的には、これはDD2に含まれる2つのトリガのうちの最初のトリガが切り替えられることを意味します。 出力DD1要素上のパルスが終了すると、次に、第2のトリガのパルスの後(負の)エッジがDD2の一部として切り替え、状態DD2を変化出力(出力Qは、D入力から読み取られた情報に表示されます)。 これは、トランジスタVT1、VT2の各々に基づくゲートパルスの出現の可能性を1周期の間に2回除外する。 実際、DD2トリガの入力Cのパルスレベルが変化するまで、その出力の状態は変化しない。 したがって、パルスは、チャネルのうちの1つ、例えば上側のもの(DD3、DD5、VT1)によってチップの出力に送信される。 入力パルスCが終了すると、DD2トリガが切り替わり、上の方をロックし、下のチャンネル(DD4、DD6、VT2)のロックを解除します。 したがって、入力Cおよび入力DD5、DD6に到着する次のパルスは、下位チャネルのチップの出力に送信される。 従って、その負エッジを有するDD1素子の出力パルスの各々はトリガDD2を切り換え、それによって次のパルスの経路を変更する。 従って、制御チップのための基準材料は、チップのアーキテクチャがダブルパルスの抑制を提供することを示している。 同じトランジスタに基づいてある期間にわたって2つのロック解除パルスの出現を除外する。

マイクロ回路のデジタル経路の1つの動作期間を詳細に検討する。

チャネルのベースにパルス上のゲートの出現は、出力トランジスタ上部(VT1)以下(VT2)及びDD3要素状態、DD4(「2-E」)の論理演算素子DD5、DD6(「2又は-NO」)により決定される順番で トリガDD2の状態によって決定される。

両方の入力が低電圧レベル(論理0)を提示する場合に知られているように論理素子2 NORは、そのような要素の出力は、単一のケース場合にハイレベル電圧(ロジック1)が表示されていること。 2つのOR-NO素子の出力における入力信号の残りの可能な組み合わせにより、低電圧レベル(論理0)が存在する。 したがって、出力Q DD2トリガロジック1(モーメントTI図図13 5)存在する場合、出力/ Q - 論理0、論理1、及び要素の入力DD3(2I)の両方で出力であろう従って論理1が現れます DD3、したがって上位チャネルのDD5(2IFI-HE)エレメントの入力の1つにも適用されます。 したがって、関係なく、出力素子DD1、DD5出力論理状態からこの要素の第2の入力に信号レベル入力のON、トランジスタVT1は閉じた状態に留まります。 DD4要素の出力の状態は論理0です。これは、 DD4の入力の1つに論理0が存在し、DD2トリガの出力/ Qからそこに来る。 DD4要素の出力からの論理0は、DD6要素の入力の1つに入力され、下位チャネルを通るパルスの通過を許可します。 この正極性パルス(論理1)を出力DD6に現れ、したがってパルスDD1出力部材との間の休止(AT VT2に基づいて、すなわち、出力論理0が存在DD1である時間 - 間隔TRT2図図13 5 )。 したがって、トランジスタVT2は開き、そのインパルスは正のレベルから下降する(共通のエミッタでスイッチを入れる場合)。

次の要素DD1出力パルス(時刻t2図図13 5)を起動すると、VT2が閉じられ、その出力論理0が表示され、従ってトランジスタでDD6素子以外デジタル回路経路の構成要素の状態を変化させません。 ( - 出力Qは、論理1 - 出力/ Q論理0)完了DD1出力パルス(時間Ta)が反転状態変化トリガDD2出力を発生します。 したがって、要素DD3、DD4(出力DD3-論理0、出力DD4-論理1)の出力の状態は変化する。 最初に始まった!要素DD1の出力での一時停止は、上部チャネルのトランジスタVT1を開く可能性を引き起こす。 DD3素子の出力における論理0は、この可能性を「確認」し、それをトランジスタVT1に基づくゲートパルスの現実の外観に変える。 このパルスはUまで持続し、VT1が終了し、プロセスが繰り返されます。

したがって、ICチップの基本的な考え方は、端子8及び11(又は端子9で及び10)の出力パルスの持続時間は、パルス出力要素DD1間の休止の持続時間によって決定される経路です。 要素DD3、DD4は、同じ信号DD1によって制御されるトリガDD2の出力Qおよび/ Qで交番する低信号によるパルスの経路を決定する。 要素DD5、DD6は、低レベルの一致方法です。

チップの機能的能力の記述を完全にするためには、チップの1つのより重要な特徴に留意する必要がある。 図の機能図から分かるように、DD3、DD4要素の入力は結合され、マイクロ回路のピン13に出力されます。 したがって、ロジック1がピン13に供給される場合、要素DD3、DD4はDD2トリガの出力Qおよび/ Qのリピータとして機能します。 この場合、素子DD5、DD6およびトランジスタVT1、VT2は、半周期の位相シフトでスイッチングされ、2ストロークハーフブリッジ回路を用いて構築されたUPSの電力セクションの動作を保証する。 論理0がピン13に供給されると、要素DD3、DD4はロックされる。 これらの要素の出力の状態は変化しません(定数論理0)。 したがって、DD1素子の出力パルスは、素子DD5、DD6に等しく影響を及ぼす。 素子DD5、DD6、したがって出力トランジスタVT1、VT2は、位相シフトなしで(同時に)スイッチングされる。 制御マイクロサーキットのこの動作モードは、UPSの電源セクションが単一サイクル方式で行われる場合に使用されます。 この場合、マイクロ回路の両方の出力トランジスタのコレクタおよびエミッタは、増幅の目的のために結合される。

プッシュプル回路の「ハード」論理単位として、出力電圧

内部ソースチップUref(チップのピン13はピン14と組み合わされる)。

次に、チップのアナログ回路の動作について考えてみましょう。

DD1の出力状態は、PWM DA2コンパレータ(図4)の出力によって決定され、DD1の入力の1つに入力されます。 第2の入力DD1に入るコンパレータDA1(図2)の出力は、通常動作時のDD1出力の状態に影響を及ぼさず、DA2コンパレータPWMのより広い出力パルスによって決定される。

さらに、図13の図は、PWMコンパレータの非反転入力(図3)で電圧レベルが変化すると、マイクロ回路(図12,13)の出力パルスの幅が比例して変化することを示しています。 通常の動作では、PWM DA2コンパレータの非反転入力の電圧レベルは、DA3エラーアンプの出力電圧によってのみ決定されます(これは、 出力電圧 増幅器DA4)に供給され、これは信号レベル フィードバック 非反転入力(マイクロ回路のピン1)に接続します。 従って、制御パルスの出力1、出力チップ幅にフィードバック信号を印加するときの順番にのでUPS出力電圧のレベルの変化に比例して変化するフィードバック信号のレベルに比例して変化するであろう フィードバックはそこから開始されます。

両方の出力トランジスタVT1およびVT2が閉じているときのチップの端子8および11の出力パルス間の時間間隔は「不感帯」と呼ばれる。

コンパレータDA1は「デッドゾーン」コンパレータと呼ばれ、 可能な最小期間を決定します。 これをより詳細に説明しましょう。

時間図から図13は、PWMコンパレータDA2の出力パルスの幅が何らかの理由低下を強制する場合は、比較器DA1の出力パルスのパルス幅で開始するPWMコンパレータの出力パルスよりも広くなり、DA2を決定することになります 論理素子DD1の出力状態、従って、 チップの出力パルスの幅。 換言すれば、比較器DA1は、チップの出力パルスの幅をある最大レベルに制限する。 制限のレベルは、定常状態の比較器DA1(マイクロ回路のピン4)の非入力側の電位の電位によって決定される。 しかし、他方では、ピン4の電位がチップの出力パルスの緯度調整の範囲を決定する。 ピン4の電位が上昇すると、この範囲は狭くなります。 最も広い調整範囲は、ピン4の電位が0のときに得られます。

しかしながら、この場合、「不感帯」の幅が0に等しくなる可能性があるという事実に伴う危険がある(例えば、UPSから消費される電流が大幅に増加した場合)。 これは、チップのピン8とピン11の制御パルスがお互いに直接続くことを意味します。 したがって、「ラックの故障」と呼ばれる状況が存在する可能性があります。 これは、インバータのパワートランジスタの慣性によって説明され、瞬時に開閉することはできません。 そのため、ファイルのロック信号とトランジスタのクローズドベース開くには、トランジスタのベースで同時に場合 - ゲート(すなわち、ゼロ「デッドゾーン」)は、あなたは一つのトランジスタがまだ閉じていない、と他のがすでに開いている状況を取得します。 次に、両方のトランジスタを通る貫通電流の流れにあるハーフブリッジのトランジスタラックには故障があります。 この電流は、図2の回路から分かるように、 5、一次巻線を通す 電源トランス 実質的に無制限です。 この場合の現在の保護は機能しません。 電流は電流センサ(図示されていないが、使用される電流センサの設計および動作原理は以下のセクションで詳細に説明する)に流れない。これは、このセンサが制御回路に信号を与えることができないことを意味する。 したがって、非常に短い時間で貫通電流が非常に大きな値に達する。 これにより、両方のパワートランジスタで放出される電力が急激に増加し、ほぼ瞬間的な故障(通常は故障)が発生します。 さらに、電流を流すことによって、電力整流器ブリッジのダイオードをディスエーブルすることができます。 このプロセスは、その慣性のために回路素子を保護する時間がなく、プライマリ・ネットワークを過負荷から保護するだけの電源ヒューズの発火で終わる。

したがって、制御電圧。 パワートランジスタのベースに供給される電流は、これらのトランジスタのうちの第1のトランジスタが確実に閉じられ、他のトランジスタのみが開くように形成されるべきである。 言い換えれば、パワートランジスタのベースに供給される制御パルスの間には、必ずゼロに等しくない時間シフト(「不感帯」)が存在しなければならない。 「不感帯」の最小許容時間は、電源スイッチとして使用されるトランジスタの慣性によって決まります。

チップのアーキテクチャにより、マイクロ回路のピン4の電位を使って「デッド・ゾーン」の最小持続時間の値を調整することができます。 この電位は、UREFチップの内部基準源の出力電圧バスに接続された外部分圧器によって設定されます。

一部のUPSバージョンでは、そのような仕切りは利用できません。 これは、(下記参照)ソフト起動処理の完了後、端末チップ4の電位がこれらの場合には0となることを意味し、「デッドゾーン」の可能な最小持続時間は、まだ0に等しくなっていないと、内部電圧源DA7によって決定されるであろう(0 コンパレータDA1の非反転入力にその正極によって接続され、マイクロ回路のピン4には負である。 したがって、これによりソースの包含にコンパレータ出力パルスDA1の幅、ひいてはない状況下で「デッドゾーン」の幅は、0に等しくなることがあり、従って、意志根本的に不可能「に検体ラックを」。 言い換えれば、マイクロ回路のアーキテクチャは、その出力パルスの最大持続時間(「不感帯」の最小持続時間)によって制限される。 出力のソフトスタータ電位の後、チップ端子4に接続された分周器が存在する場合、端末4における(ソフトスタート処理後)、残留しかし、電位比較器DA1の出力パルスの幅がないだけ内部ソースDA7によって決定されるように、0に等しくないが、 この場合、上述したように、コンパレータDA2の緯度PWM制御のダイナミックレンジが狭くなる。

START-UP SCHEME

始動回路は、TTIを電源ネットワークに回した後に始動するために制御チップに給電するのに使用できる電圧を生成するように設計されている。 このため、始動手段は、電源部と全体としてすべてのUPS回路を動作させることができないが正常に機能せず、第一の制御チップを動作するように開始します。

スタートアップ回路は、2つの異なる方法で構成することができます。

自己励起で;

強制的な興奮で。

自己励磁回路は、例えばGT-150W UPS(図14)で使用されます。 Uepネットワークの整流された電圧は、両方のパワーキートランジスタQ1、Q2のベースである抵抗分割器R5、R3、R6、R4に供給される。 したがって、コンデンサの両端の総電圧の影響C5下トランジスタを介して、C6(UEP)(+)回路のベース電流が流れ始めるC5 - R5 - R7 - 6-E Q1 - R6 - R8 - 6-E Q2 - "共通配線" の一次側 - ( - )C6。

両方のトランジスタはこの電流によってわずかに開かれている。 その結果、互いに反対方向の電流が、回路に沿って両方のトランジスタのコレクタ - エミッタのセクションを通って流れ始める。

Q1:(+)C5-バス+ 310V-k-e Q1-5-6 T1 -1-2 T2-C9-( - )C5。

Q2を介して:(+)C6 - C9 - 2-1 T2 - T1 6-5 - E K-Q2 - "共通線" の一次側 - ( - )C6。

図14. GT-150Wの自己励磁による起動回路

追加の(開始)巻線5-6T1を逆方向に流れる両方の電流が等しい場合、結果の電流は0に等しく、回路は始動できなかった。

しかし、トランジスタQ1、Q2の電流利得の技術的な広がりにより、これらの電流のうちの1つは常に他のものよりも大きい。 トランジスタは多少変化する程度に開いている。 したがって、巻線5-6T1を通る合成電流は、0に等しくなく、この方向またはその方向を有する。 電流がトランジスタQ1を介して支配的である(Q1がQ2よりも若干開いている)と仮定すると、電流は端子5から端子6の方向に流れる。 さらなる推論はこの仮定に基づいている。

しかし、公平には、電流がトランジスタQ2を介して支配的であり、さらに説明されるすべてのプロセスがトランジスタQ2を参照することに注意すべきである。

巻線5-6T1を流れる電流は、制御変圧器T1のすべての巻線にEMF相互誘導の発生を引き起こす。 D7-R9-R7-6-3 Q1 - - 5 T1従って(+)EMFは起電力の流れの影響を受けて出力5とQ1のベースに対して端末4に表示され、さらに、その電流回路4 T1上に開口しています。

同時に、端末7T1では、端末8に対して( - )emfが現れる。 このEMFの極性がQ2のためにロックされていることが判明し、それが閉じます。 次は正帰還(PIC)です。 その作用は、Q1のコレクタ - エミッタ部を通る電流増加及びT1はT1の巻線4-5に5-6コイルとQ1のための追加のベース電流を生成することにより、さらに多くのことが開き、EMFを増加させる作用することです。 このプロセスは、アバランシェのような(非常に迅速な)発展をもたらし、Q1の完全な開放およびQ2のロックにつながる。 開路Q1および電力パルストランスT2の一次巻線1-2を介して、直線的に増加する電流が流れ始め、これによりすべての巻線T2に相互誘導のEMFパルスが発生する。 巻線7-5T2からのパルスは蓄積容量C22を充電する。 C22では電圧が現れ、TL494タイプのIC1制御チップの出力端子12と整合段に電源として供給される。 チップが起動し、その端子11,8に矩形パルスシーケンスを生成し、これを介してパワーキーQ1、Q2がマッチングステージ(Q3、Q4、T1)を介してスイッチを開始する。 電源トランスT2のすべての巻線に、パルス化されたemfs 名目レベルの。 同時に、巻線3-5および7-5からのEMFは、それに変化しない電圧レベル(約+ 27V)を維持しながら、常にC22に給電する。 言い換えれば、フィードバックリング上のマイクロ回路はそれ自身の記録を開始する(自己フィード)。 ユニットは動作モードに入ります。 マイクロ回路と整合段の電源電圧は補助的であり、ユニット内部でのみ動作し、通常はウオームと呼ばれます。

この方式は、コンピュータ位Mazovia SM1914(図15)のためのLPS-02-150XTパルス電源(台湾の製造)のようないくつかの品種を有することができます。 この方式では、起動プロセスの開発のための最初の推進力は、別個の半波整流器、抵抗分圧器を切り替える電源の基本的なネットワークの最初の正の半サイクルを付勢D1、C7、によって得られます。 これにより、起動プロセスが高速化されます。 高容量の平滑コンデンサの充電と並行して、キーのうちの1つの初期ロック解除が行われる。 他の点では、回路は上述したのと同様の仕方で動作する。

図15.パルス電源での自己励磁による起動回路LPS-02-150XT

このような回路は、例えばLING YIN GROUP(台湾)のPS-200BのUPSに使用されている。

特殊始動トランスT1の一次巻線は、主電源電圧の半分(定格220V)またはフル(110V定格)にスイッチオンされる。 これは、二次巻線T1の交流電圧の振幅が供給ネットワークの公称値に依存しないという考察から行われる。 一次巻線T1を通して、UPSがオンになると、 交流。 したがって、二次巻線3-4T1上では、電源の周波数を有する交番正弦波EMFが誘起される。 このEMFの影響下に流れる電流は、ダイオードD3-D6上の特別のブリッジ回路によって整流され、コンデンサC26によって平滑化される。 C26では、約10-11Vの定電圧が割り当てられ、TL494タイプのU1制御チップの出力12および整合段に電源として供給される。 このプロセスと並行して、平滑化フィルタのコンデンサが充電される。 したがって、マイクロ回路に電力が供給されるときまでに、電力カスケードにも通電される。 マイクロ回路が起動され、端子8,11列の矩形パルスの生成が開始され、これを介して電源キーが一致するカスケードを介してスイッチを開始する。 その結果、ブロックの出力電圧が現れます。 自己給電モードに入った後、デカップリングダイオードD8を介して+ 12V出力バスからマイクロ回路が作られる。 この自己給電電圧は整流器D3~D5の出力電圧よりわずかに高いので、この始動整流器のダイオードはロックされており、将来は回路の動作に影響を与えない。

D8ダイオードによるフィードバックの必要性は必須ではありません。 強制励起が使用されるいくつかのUPSの方式では、この接続は存在しません。 制御マイクロサーキットとマッチングカスケードは、全動作時間中に起動整流器の出力から供給されます。 しかし、この場合のUpomバスのリプル・レベルは、+ 12Vの出力電圧バスからのチップの電源の場合よりも多少高くなります。

スタートアップスキームの説明を要約すると、それらの構築の主な特徴に注目することができます。 自己励振回路では、パワートランジスタの初期スイッチングが行われ、その結果、Upomチップの電源電圧が発生します。 強制励起回路では、まず、Upomが得られ、その結果、パワートランジスタのスイッチングが行われる。 さらに、自己励振電圧を持つ回路では、通常、Upomは約+ 26Vのレベルを持ち、強制励起の回路では約+ 12Vです。

強制励磁方式(別の変圧器を用いた方式)を図5に示す。

図16.強制励起による開始の仕組み インパルスブロック 電源装置PS-200B(LING陰性グループ)。

PULSE POWER SUPPLY UNITの契約カスケード

パワフルな出力段と低電力制御回路を調整してデカップリングするには、一致するカスケードが機能します。

異なるUPSに一致するカスケードを構築するための実際的な手法は、2つの主要な変形に分けることができます。

トランジスタ・バージョンでは、外部トランジスタが個別設計の個別キーとして使用されます。

非トランジスタバージョンであり、制御チップVT1、VT2(積分バージョン)の出力トランジスタがキーとして使用される。

さらに、マッチング段階を分類することが可能な別の特徴は、ハーフブリッジインバータのパワートランジスタを制御する方法である。 これに基づいて、すべての連結カスケードは以下のように分けられます。

両方のパワートランジスタの制御が1つの1次巻線と2つの2次巻線を有する1つの共通制御トランスを使用して実行される共通制御のカスケード。

個別の制御を有するカスケードであり、各パワートランジスタは、別個の変圧器、すなわち、 マッチング段階では、2つの制御トランスがあります。

両方の分類に基づいて、マッチングステージは次の4つの方法のいずれかで実行できます。

共通制御のトランジスタ;

別個の制御を有するトランジスタ;

一般的な制御の非トランジスタ;

別々の制御を有する非トランジスタ。

別々の制御を持つトランジスタカスケードはまれに使用されるか、まったく使用されません。 著者らは、一致するカスケードのそのような実施形態に遭遇する機会を持っていなかった。 他の3つのオプションは多かれ少なかれ共通です。

いずれの場合も、電源カスケードへの接続はトランス方式で行われます。

この場合、変圧器は、電流による制御信号の増幅(電圧による減衰による)とガルバニック絶縁の2つの主な機能を果たします。 ガルバニック絶縁が必要なのは、制御用マイクロ回路と整合段が2次側にあり、電源カスケードがUPSの1次側にあるためです。

特定の例についてマッチング段階の各変形の動作を考える。

共通の制御を有するトランジスタ方式では、トランジスタQ3およびQ4上の2段階トランス電力プリアンプが整合段として使用される(図17)。

図17. KYP-150Wスイッチング電源カスケード(汎用トランジスタ回路)

図18.コレクタのインパルスの実際の形式

ダイオードD7およびD9を通る電流は、コアDTに蓄積された磁気エネルギーの影響下で流れ、減衰する指数の形態を有する。 DTのコアでは、電流の流れの間に、変化する(減少する)磁束がダイオードD7およびD9を介して作用し、その結果、 二次巻線.

ダイオードD8は、共通の電源レールを介して制御IC上の整合段の影響を排除します。

ESAN ESP-1003Rスイッチング電源(図19)では、共通の制御を備えた別のタイプのトランジスタマッチングカスケードが使用されています。 このオプションの第1の特徴は、チップの出力トランジスタVT1、VT2がエミッタフォロワとして含まれることである。 出力信号は、マイクロ回路の端子9,10から取り出される。 抵抗器R17、R16およびR15、R14はそれぞれトランジスタVT1およびVT2のエミッタ負荷である。 これらの抵抗は、キーモードで動作するトランジスタQ3、Q4の基本分圧器を形成します。 容量C13およびC12は、トランジスタQ3およびQ4のスイッチングプロセスを強制し、加速する。 このカスケードの第2の特徴は、制御変圧器DTの一次巻線が中間点からの出力を持たず、トランジスタQ3、Q4のコレクタ間に接続されていることである。 制御チップの出力トランジスタVT1が開くと、トランジスタQ3分圧器R17、R16のための基本的な電圧Upomによって電力が供給される。 したがって、制御遷移Q3を通って電流が流れ、それが開く。 このプロセスの加速は、ゲート電流のベースQ3への供給を提供する昇圧キャパシタンスC13に寄与し、これは定常値よりも2~2.5倍高い。 開口Q3の結果は、一次巻線1-2 DTが端子1によって本体に接続されていることである。 第2のトランジスタQ4がロックされているので、増加する電流が一次巻線DT:Upom-R11-2-1 DT-koe Q3-の場合に流れる。

図19.インパルス電源のマッチングカスケードESP-1003R ESAN ELECTRONIC CO。、LTD(共通制御のトランジスタ方式)。

二次巻線3-4および5-6には、矩形のemfのパルスが現れる。 二次側DT巻線の巻き方向は異なる。 したがって、パワートランジスタ(図示せず)のうちの1つは、開口基本インパルスを受け取り、他方は、閉じたものを受け取る。 制御チップのVT1が閉じられると、Q3もまた制御チップの後に閉じる。 昇圧コンデンサC13によって閉路プロセスの加速が促進され、昇圧コンデンサC13の電圧は閉極極性のベース - エミッタQ3の遷移に印加される。 さらに、「デッドゾーン」は、マイクロ回路の両方の出力トランジスタが閉じられたときにも続く。 次に、出力トランジスタVT2が開き、通電されたUpom電圧が第2のトランジスタQ4分圧器R15、R14の基本であることがわかる。 したがって、Q4が開き、一次巻線1-2 DTが他端(ピン2)で本体に接続されているため、前のケースとは逆方向の増加電流が回路を流れ始める:Upom -R10- 1-2 DT-koe Q4- "身体"。

従って、二次巻線DT上のパルスの極性は変化し、開路パルスは第2のパワートランジスタを受け取り、第1のパルスに基づいて閉路極性が作用する。 制御チップのVT2が閉じられると、(昇圧コンデンサC12の助けを借りて)Q4もそれの後に閉じる。 そして再び、「不感帯」が続き、その後、プロセスが繰り返される。

従って、このカスケードの仕事に埋め込まれている主要なアイデアは、一次巻線DTが一端または他端によってケーシングに接続されているために、DTのコア内の可変磁束が得られることである。 したがって、ユニポーラ電力を有する一定の成分なしに交流電流が流れる。

マッチング段のトランジスタとしてのUPSの整合段の非トランジスタ変形例では、前述したように、制御マイクロ回路の出力トランジスタVT1、VT2が使用される。 この場合、整合段の個別のトランジスタは存在しない。

非同相モード同相回路は、例えばPS-200B UPS方式で使用されます。 VT1、VT2チップの出力トランジスタは、DTトランスの1次側半巻線によってコレクタに沿って負荷されます(図20)。 一次巻線DTの中心点に電力が供給される。

図20. PS-200Bスイッチング電源のカスケードの整合(非トランジスタ方式と共通制御)。

トランジスタVT1が開くと、制御トランスDTのこのトランジスタおよび半巻線1-2を通って増加する電流が流れる。 DT制御巻き線は、インバータのパワートランジスタの1つが開き、他の1つが閉じるような極性で、DTの2次巻線上に現れる。 完了時VT1パルスが突然閉じ、poluobmotku 1-2 DTを介して電流が流れなくなるので、起電力が二次巻線パワートランジスタの閉鎖につながるDT、で消滅します。 さらに、「デッドゾーン」は、マイクロ回路の出力トランジスタVT1、VT2の両方が閉じられ、一次巻線DTを流れる電流が流れないときに持続する。 次に、トランジスタVT2が開き、時間とともに増加する電流がこのトランジスタを通って流れ、2-3T DTを半巻線する。 DTのコアにおけるこの電流によって生成される磁束は、前の場合とは反対の方向を有する。 したがって、二次巻線では、前の極性の場合と逆のDT emfsが誘起される。 その結果、ハーフブリッジインバータの第2のトランジスタが開かれ、第1のトランジスタに基づいて、パルスはそれを閉じる極性を有する。 制御チップのVT2が閉じられると、それを流れる電流と一次巻線DTが停止する。 したがって、二次巻線DT上でEMFが消滅し、インバータのパワートランジスタが再び閉じられる。 そして再び、「不感帯」が続き、その後、プロセスが繰り返される。

このカスケードの構成の基本的な考え方は、変圧器の制御コアに交番磁束が変圧器の一次巻線の中点に電源を供給することによって得ることができることです。 したがって、電流は、異なる方向に同じ巻き数の半巻線を通って流れる。 出力トランジスタ回路の両方が(「デッドゾーン」)を閉じている場合、コアDT 0交互トランジスタにおける磁束は、一方または他方poluobmotkiの磁束の様子を代替開口を引き起こします。 得られたコア中の磁束は、変化させることによって得られる。

これらの品種のうちの最後のもの(別個の制御を有する非トランジスタ方式)は、例えば、Appisコンピュータ(ペルー)のUPSにおいて使用される。 この回路には、2つの制御トランスDT1、DT2があり、その1次巻線は、マイクロサーキットの出力トランジスタのコレクタ負荷である(図21)。 この方式では、2つの電源スイッチのそれぞれが別のトランスを介して制御されます。 電力は、チップの出力トランジスタのコレクタに、共通のUpomバスから制御トランスDT1、DT2の一次巻線の中間点を介して供給される。

一次巻線DT1、DT2の対応する部分を有するダイオードD9、D10は、コアの減磁回路を形成する。 この問題について詳しく説明しましょう。

図21.インパルス電源「Appis」のカスケードの一致(別の制御を持つ非トランジスタ方式)。

マッチングカスケード(図21)は本質的に2つの独立した単一サイクル順方向トランスデューサであり、 整合トランジスタの開放状態の間にパワートランジスタのベースに開口電流が流れる。 整合トランジスタとトランスを介して接続されたパワートランジスタは同時にオープンします。 同時に、両方 パルストランス DT1、DT2は、一次巻線電流の一定成分、すなわち、 強制バイアス付き。 あなたはコアを消磁するために特別な措置を提供しない場合、それらは、一次巻線のインダクタンスを大幅に削減し、スイッチングトランジスタVT1、VT2の故障につながるコンバータのいくつかの期間、磁気飽和を入力します。 トランジスタVT1とトランスDT1上のコンバータで発生するプロセスを考えてみましょう。 トランジスタVT1が開かれ、それと1次巻線1-2 DT1を通ると、線形に増加する電流が回路:Upom -2-1 DT1-k-e VT1-「body」を流れる。

VT1ベースのゲートパルスが終了すると、急激に閉じます。 巻線1-2のDT1を通る電流は停止する。 Upom - - C9「ボディ」 - D10-3DT1しかしDT1 2-3請求変化の極性を巻消磁にEMF、この介して巻線とダイオードD10は、DT1 2 DT1コア回路における電流消磁流れます。

この電流は直線的に減少する。 コアDT1を通る磁束の導関数が符号を変え、コアが減磁される。 したがって、この逆サイクルの間に、トランジスタVT1の開状態の間にコアDT1に蓄積された余分なエネルギーがソースに戻される(Upam蓄積コンデンサC9は充電される)。

しかしながら、マッチング段階のそのような実施形態は、 両方の変圧器DT1、DT2は誘導によって、また一次巻線電流の一定成分を用いて十分に活用されないように働く。 コアDT1、DT2の反転は、特定のサイクルで起こり、正の誘導値のみをカバーする。 このため、コア内の磁束は脈動するようになる。 定数コンポーネントを含みます。 これは、変圧器DT1、DT2の過大な質量パラメータにつながり、さらに、整合段の他の変種と比較して、ここでは1つではなく2つの変圧器を必要とする。

| IBMのパルス電源の主なパラメータ | スイッチング電源の主なパラメータを考慮し、コネクタのピン配置を示し、動作原理は主電源電圧110および220ボルト、 | |||

| TL494チップ、配線図、およびスイッチング電源の電源スイッチを制御するためのユースケースの詳細な説明。 | ||||

| TL494を介したパルス電源ユニットの電源キーの管理 | スイッチング電源のパワートランジスタの基本回路を制御する基本的な方法、二次電源用の整流器の構成の変形例について説明する。 | 完全な説明 概念的枠組み スイッチング電源装置の動作 | ||

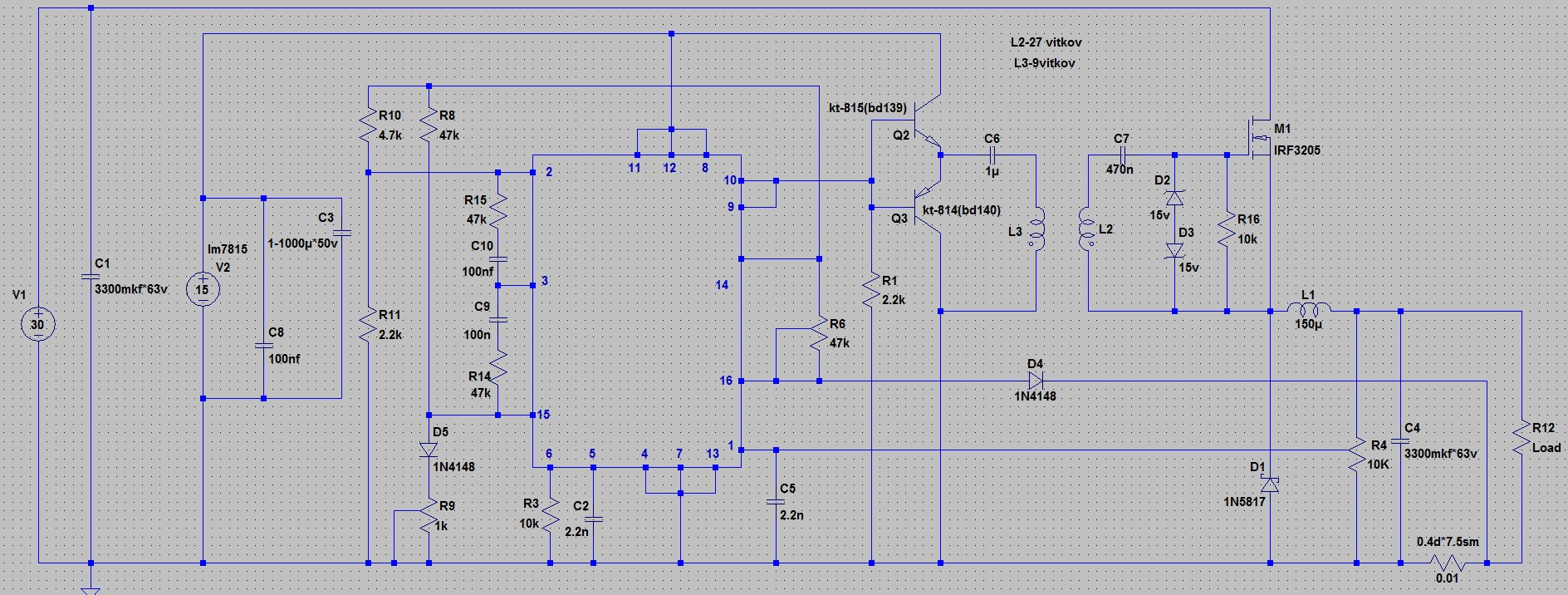

私はインターネットをサーフィンし、電圧レギュレータ回路は見つけられず、最も重要なのは現代の要素ベースです。 それらのすべて

アナログまたは バイポーラトランジスタ、主要な包含で。 私はそのうちの1つを試しました。

電流は2.5アンペア以上であり、トランジスタKT818を著しく加熱することなく、私は受け取らなかった。 約4アンペアを除去しようとすると、トランジスタとショットキ・ダイオードが焼損します。 私たちは明確にする必要があります - 彼らはラジエータなしでした。 しかし、それは状況を変えない。 Pチャンネルのフィールドドライバをこのインクルードに適用する方法を反映して、彼の作品の記述が出てきました。 開放遷移時の大きな抵抗に起因する熱放散は大きすぎます。効率の良さを忘れる可能性があります。 トップキードライバによって制御されるNチャネルフィールドドライバを使用することが決定されました.

このスキームは、作業しても効率は良いが、依然として欠点があった。 彼はそれを使用して電池を充電しました。 彼らは、上部のキーが閉じられたときに下部のキーが常に開いているという事実に関連していました。 スロットルのエネルギーがなくなると、バッテリーからの電流が反対方向にスロットルを通り、下部のキーを燃焼させます。 上の方は、短絡した下部の開口部で燃えるでしょう。

同期キーを放棄し、古いショットキーダイオードを使用することが決定されました。

長い検索、試行錯誤、燃え尽きた超小型回路と現場作業員の結果、この計画が生まれました

主な特徴。

1.安定して動作します。

優れた電流と電圧を保持します。

3.効率は約90%です。 時には最大94!

4.すべての詳細がダンプの上に横たわっています。

5.実質的にチューニングする必要はありません。

6.非常に単純で繰り返し可能です。

7.電流はゼロからユーザーが望む量まで調整可能です。

8.電圧は2.5Vから調整可能です。

機能のうち。

出力電流はシャントによって制御されます。

その抵抗は約0.01オームです。 その上の熱放散は比較的小さい。 電流は広い範囲で規制されています。 0アンペアから....どのくらいキーがダイオードとスロットルを許可するか。 最大電流制限(および 短絡)は、抵抗R6によって設定される。 直ちに4アンペア以下の予約をしてください。 電流監視の特徴は、ダイオードD4に実装された「シャント・ボルトドップップ」の使用です。 これにより、TLはゼロに近い電流で正しく動作し、(抵抗R9で)短絡電流....例えば1mAを暴露することができます。 ダイオードD5は、電流制御回路の熱安定化を行う。

シャントはもともと長さが約4.5cm、直径が0.4mmの銅線であった。 銅は熱安定性が非常に悪く、加熱すると電流が浮かび上がるので、中国のマルチメーターを選ぶことに決めました。 そこから引き出されたシャントは半分に短縮され、ボードにはんだ付けされました。

スロットル

コンピュータBPから黄色と白のリングに巻きつけられた。 直径2mmのワイヤーを約24巻き巻いています。 電線をコンピュータのUPSトランスから巻き取った。

このようなワイヤでのみ5A以上の電流でスロットルが過度に加熱されるのを防ぐことができました。

強調表示はトランスドライバーキーです。 彼のためにサイトからのLiveMakerへの感謝 マイクロスマート 。 ほとんどすべてのフェライトリングで作られています。 理想的には - ブランド2000 直径2cmから。 インパルスフィルターのワイヤーから取り除かれたリングも機能します(しかし、そのほとんどが分かりませんが)。 私は既に複写機ボードを接続するワイヤーハーネスから取り除かれたリングに2枚の板を使っています。 唯一の、そしてまだマイナスの結果につながっていないのは、スイッチング信号の台形境界でのマイナスエミッションです。 これらは大きくはなく(2-3V)、デバイスの性能には影響しません。 巻き線には何も複雑ではありません。 彼はコイルの方に目を向ける。 2つのコイルのコイルをリングに沿って均等に分配してください。 一次巻線は9ターンの巻線を含む。 セカンダリ - 27ターンのワイヤ。 私は1つの住宅の通常のツイストペアをハッキングしています。 ゲート上の電圧は12-15ボルトの2つのツェナーダイオードに制限されている。 運転手はIRF3205フェンダーを簡単に揺する。 シャッターのパルスの正面は約168nSです。

逆ダイオードとして、コンピュータBPから強力なショットキーダイオードを使用した。 これは、絶縁スペーサを介して電界効果トランジスタと一緒に、コンピュータのCPUから放射器上に置かれる。

それをエッチングし、テストした。 注 - 抵抗R14とR12は実際には抵抗とコンデンサで構成されています。 ちょうど再怠惰。

現在のレギュレーションモードはシャントの抵抗の影響を非常に受けやすいため、ユニットには1次側の調整が必要です。 それは必要な抵抗R6の設置にある。 このような抵抗を選択する必要があります。電流調整ノブ(R9)を回すと必要な最大電流(4-20A)が得られます。 最大出力電流を頻繁に変更する必要がある場合は、一定の定数の代わりに可変抵抗を使用できます。 この目的のためのボード上の場所と連絡先は次のとおりです。

線形スタビライザLM7815をパルスMC34063に変更する計画では、LM7815が24Vを超える電源電圧で非常に高温になるため、効率が低下するためです。

写真。 それははんだ付け試験によって非常に殴られます。

私はアルカリ電池の電源を充電して試験するために自分自身を収集しました。 デッドPC電源から。 最大電流 (私は十分な電流を持っている間にそれを決めた) - 20A。 私は通常、最大10A、18Vを使います。 合計 - 180ワット。 中吹きで それは24時間にわたって24時間働いています。

- < Назад

- フォワード\u003e

コメント

1 2 3 4 5 6 7 8 9 10 11»

0 #203 Michael 19/04/2017 10:46

一般的に、偶数動作LM-KE最大充填ツェナーATでわずかに(50度まで)ウォーミングアップことを観察しました。 ゲートトランス(巻線35から15)を巻き戻し、加熱はスタビライザーがスキームのとヒントのために)通常の飛行までの著者のおかげで動作します残っています!

私が使用したリング(ハーネス付き)プリンタは、私は覚えていないかどうかモニターが、絵の記事のそれよりも少しのサイズのいずれかから削除されます。

0 #202 スーパーユーザー04/17/2017 10:45 PM

論理的に考えると、7815は入力電圧の超過、または出力電流の超過を殺すことができます。 私達が得ることができない27ボルトの供給で入力電圧を超過してください(印刷が私の計画に厳密に従っている場合)。 出力電流を超えます。 あなたは自分自身でブレークダウンが観察されたことを指摘しました 最大応力 または電流。 これは、パルスの充填が最大であったことを意味する。 小さいKzapのコア(不適切な寸法または材料のもの)は、通常のように感じられ、充填が増加するとコアが飽和し、電流が急激に増加します。 私はこれを見ていないが。 良質の印刷物を写真に置きます。フォーラムで写真をアップロードできます。

0 #201 Michael 15/04/2017 09:24

4回目には、線形スタビライザが破れます。 私の理由を理解することはできません、私はゲート回路にツェナーダイオードを吸うために、最大電圧または電流の開始を示すときことに気づくまでに、最初のすべてで正常に動作して、症状が常に1と同じであり、2 lm7815を殺し、そして2つのLM317Tました。 私は電源電圧tl494を測定し、それが25ボルトの入力電圧に等しいことを確認し、スタビライザが貫通して、それを再び変化させます。

入力電圧は25-27ボルトで、過熱しないので、放熱器にかかる費用がかかります。

周波数とデューティ・サイクルを調整したTL494用ジェネレータ

実験やチューニング作業を行うための非常に便利なデバイスは、周波数ジェネレータです。 その要件はわずかです。

- 周波数調整(パルス繰り返し周期)

- デューティサイクルの調整(デューティサイクル、パルス長)

- 広い範囲

発生器の周波数範囲は非常に高く、数十ヘルツから500kHz、場合によっては1MHzまではチップに依存しますが、メーカーによって異なる可能性のある最大周波数の異なる実際の値があります。

スキームの説明に進みましょう:

Pet±and Peat〜 - 回路のデジタル部分に一定の電力を供給します 交番電圧 16~20ボルトである。

Vout - 電源セクションの電源電圧で、発電機の出力に12ボルトから供給されます。 この電圧から回路のデジタル部分に電力を供給するためには、VoutとPeat±を極性(16ボルト)で接続する必要があります。

OUT(+ / D) - 極性を考慮して、発電機の出力。 電界効果トランジスタの+ - プラス電源、D - ドレイン。 負荷が接続されています。

G D S - 電界効果トランジスタを接続するネジ端子。周波数とパワー要件に応じて選択します。 プリント回路基板のレイアウトは、出力キーに対する導体の最小長さと必要な幅を考慮して行われます。

コントロール:

Rtは発電機の周波数範囲を制御するための可変抵抗器で、その抵抗は特定の要件に合わせて選択する必要があります。 オンライン計算機TL494は以下に添付されています。 抵抗R2は、チップの時間遅延抵抗の最小抵抗値を制限します。 これはチップの特定のインスタンスに対して選択することができ、図のように配置することができます。

Ctは周波数設定コンデンサで、再び オンライン計算機。 調整範囲を要件に合わせて設定できます。

Rdtはデューティ・サイクルを調整するための可変抵抗器です。 抵抗R1は調整範囲を1%から99%に正確に調整することができ、代わりに最初にジャンパを入れることができます。

| Ct、nF: | |

| R2、kOhm: | |

| Rt、kΩ: |

スキームの仕事についてのいくつかの言葉。 マイクロコントローラの13番目の出力(出力制御)にローレベルを供給することにより、シングルサイクルモードに切り替わります。 マイクロチップの下側回路には抵抗R3が負荷され、周波数計ジェネレータに接続するための出力を生成する 周波数計)。 チップの上側のトランジスタは、電力出力トランジスタのゲートを制御するタスクである、S8050およびS8550トランジスタの相補型ペアでドライバを制御します。 抵抗R5はゲート電流を制限し、その値は変更可能である。 L1チョークと47nコンデンサは、ドライバからの干渉の可能性からTL494を保護するフィルタを構成します。 スロットルのインダクタンスは、周波数範囲に合わせる必要があります。 S8050とS8550は十分な出力とスピードを持っているため、偶然に選択されないことに注意する必要があります。これにより、前面の必要な急峻性が保証されます。 ご覧のとおり、このスキームは非常にシンプルで、同時に機能的です。

可変抵抗器Rtは、周波数調整の円滑さと精度が必要な場合は、単ターンとマルチターンの2つの直列抵抗の形で構成する必要があります。

印刷回路基板は、伝統に従って、 フェルトチップで描き、硫酸銅でエッチングする.

パワートランジスタとしては、 fET電圧、電流、周波数に適しています。 これらは、IRF530、IRF630、IRF640、IRF840です。

開いた状態のトランジスタの抵抗が低いほど、動作中の熱は少なくなります。 それにもかかわらず、ラジエーターの存在は必須です。

フライヤーが提供する計画に従って組み立てられ、検証されます。

一般的な説明と使用

TL 494 およびその次のバージョンは、2チャンネル電力変換器を構築するために最も一般的に使用されるマイクロ回路である。

- TL494(テキサス・インスツルメンツの独自開発品) - シングルエンド出力付きPWM ICコンバータ電圧(TL 494 IN - ケースDIP16、-25..85C、TL 494 CN-DIP16、0.70C)。

- K1006EU4 - TL494の国内アナログ

- TL594 - 誤差増幅器とコンパレータの精度を改善したアナログTL494

- TL598 - 出力にプッシュプル(pnp-npn)リピータ付きアナログTL594

この材料 - オリジナルの技術的な話題の合成 Texas Instruments 、出版物International Rectifier(「パワー半導体デバイスInternational Rectifier」、Voronezh、1999)およびモトローラ。

このチップの利点と欠点:

- プラス:開発された制御回路、2つの差動アンプ(両方のロジック機能を実行可能)

- マイナス:単相出力は追加取り付けが必要です(UC3825と比較して)

- 少ない:電流制御なし、比較的遅いフィードバックループ(自動車用PNでは重要ではない)

- マイナス:2つ以上のICをCinchronicに組み込むことは、UC3825ほど便利ではありません

1. TL494の特長

ION回路と低電圧保護。 電源が5.5〜7.0 Vのスレッショルド(標準値は6.4V)に達すると、回路がオンになります。 この時点まで、内部制御バスは、発電機および回路の論理部分の動作を禁止する。 + 15V電源電圧での無負荷電流(出力トランジスタはディスエーブルされています)は10mA以下です。 ION + 5V(+ 4.75〜+ 5.25V、出力安定化は+/- 25mVより悪くありません)は、最大10mAのアップストリーム電流を供給します。 IONはNPNエミッタフォロワー(TIの19-20ページ参照)を使用することによってのみ使用できますが、このような「スタビライザー」の出力では、電圧は負荷電流に強く依存します。

発電機 TL494テキサス・インストゥルメンツではランプ電圧0 .. + 3.0V(IONで指定された振幅)、モトローラTL494では0 ... + 2.8V(他のものから何を期待するか)をTI F = 1.0 /(RtCt)であり、F = 1.1 /(RtCt)である。

1〜300 kHzの動作周波数が推奨され、推奨範囲はRt = 1〜500kΩ、Ct = 470pF〜10μFです。 この場合、周波数の典型的な温度ドリフトは+/- 3%(ヒンジ付き部品のドリフトを考慮せず)であり、電源電圧に依存する周波数偏差は許容範囲全体で0.1%以内です。

ジェネレータを遠隔からスイッチオフするには、入力Rt(6)を外部キーを使用してION出力にクローズするか、Ctをグランドに近づけます。 もちろん、Rt、Ctを選択するときは、オープンキーの漏れ抵抗を考慮する必要があります。

休止相(デューティサイクル)の制御の入力は、 残りの位相比較器を介して、回路のアームのパルス間に必要な最小休止時間が設定される。 これは、IC外部の電源カスケードのエンドツーエンド電流を防止し、トリガの安定動作のために必要です。TL494のデジタル部のスイッチング時間は200nsです。 CTのソーが制御入力4(DT)の電圧を超えると、出力信号がイネーブルされます。 制御電圧がゼロで最大150kHzのクロック速度では、残りの位相=周期の3%(制御信号の等価オフセットは100.120mV)であり、大きな周波数では、内蔵補正によって静止位相が200.300nsに拡大されます。

DT入力回路を使用して、固定位相(R-Rデバイダ)、ソフトスタート(R-C)モード、リモートシャットダウン(キー)を指定し、リニア制御入力としてDTを使用できます。 入力回路はpnpトランジスタで構成されているため、入力電流(1.0μAまで)がICから流れ出して流れません。 電流は十分に大きいので、高抵抗の抵抗(100kΩ以下)は避けるべきです。 TIの23ページに、3ピンツェナーダイオードTL430(431)を使用した過電圧保護の例を示します。

アンプのエラー 実際には、一定電圧(初期のシリーズでは60dB)でKu = 70..95dB、350kHzでKu = 1の演算増幅器。 入力回路はpnpトランジスタで構成されているため、入力電流(1.0μAまで)はICから流れ出し、ICに流れません。 電流はオペアンプにとって十分に大きいので、バイアス電圧も(最大10mV)であるため、制御回路の高抵抗抵抗(100kΩ以下)は避けるべきです。 しかし、pnp入力を使用するため、入力電圧の範囲は-0.3V〜V電源-2Vです。

2つの増幅器の出力は、ダイオードORによって結合される。 増幅器の出力端には、 より大きなストレスロジックの制御をインターセプトします。 この場合、出力信号はダイオードORの出力(エラーコンパレータの入力でもあります)からのみ、別途ではなく使用できます。 したがって、線形モードのOSループによって1つの増幅器のみを閉じることができます。 このアンプは、出力電圧によってメインのリニアOSを閉じます。 前記第2の増幅器は、比較器として使用することができる - 例えば、出力電流を超えた、または論理アラーム信号(過熱、短絡、等)、リモートシャットダウンするためのキーとして、等の比較器の入力の1つがイオンに結び付けられている、第二の論理上に配置され OR警報(さらに良い - 通常の状態の論理AND信号)。

RC周波数依存OSを使用する場合、増幅器の出力は実際にはシングルエンド(直列ダイオード!)であることを覚えておいてください。したがって、充電は充電されますが、放電するには時間がかかります。 この出力の電圧は0〜+ 3.5V(発電機のスパンよりわずかに大きい)の範囲にあり、電圧比が急激に低下し、出力で約4.5Vになると、アンプは飽和します。 同様に、アンプの出力回路(ループOC)の低抵抗の抵抗は避ける必要があります。

アンプは、動作周波数の1クロック・サイクル内で動作するようには設計されていません。 増幅器内部の信号の伝搬が400nsである場合、これらの信号は遅すぎるため、トリガ制御ロジックは許容しません(出力にサイドインパルスが存在します)。 実際のPN回路では、フィードバック回路のカットオフ周波数は200-10000Hzのオーダーになるように選択されます。

トリガおよびロジック制御出力 - 場合、電源電圧以下7B、電圧は誤差増幅器(埋め込みしきい値とオフセットを考慮して)のいずれかでブレードよりも大きい場合、制御入力DTよりも発電機ブレードの電圧が、そして場合 - 出力回路を可能にしました。 ジェネレータが最大からゼロにリセットされると、出力は切断されます。 準相出力を有するトリガは、周波数を2つに分割する。 入力13(出力モード)のロジック0では、トリガ・フェーズはORで結合され、両方の出力に同時に適用されます。ロジック1は各出力に対して別々に適用されます。

出力トランジスタ - npn熱保護機能を内蔵したダーリントン(電流保護機能はありません)。 したがって、コレクタ(通常は正のバス上に閉じられる)とエミッタ(負荷上)との間の最小電圧降下は1.5V(標準で200mA)であり、共通エミッタを持つ回路ではわずか1.1Vです。 制限された出力電流(1つのオープン・トランジスタによる)は500mAに制限されており、クリスタル全体の制限電力は1Wです。

2.アプリケーションの機能

MISトランジスタのゲート上で作業する。 出力リピータ

MISトランジスタのゲートである容量性負荷で動作するとき、出力トランジスタTL494は、エミッタフォロワによってオンにされる。 200mAの平均電流の制限により、回路はシャッターを十分に高速で充電することができるが、トランジスタをオフにして放電することは不可能である。 シャッターを接地された抵抗器で放電してください。 結局のところ、従来のゲート容量の電圧は指数関数的に減少し、トランジスタを閉じるためには、ゲートは10Vから3V以下に放電されなければならない。 抵抗器を通る放電電流は、トランジスタを通る電荷の電流よりも常に小さくなります(抵抗器は長時間加熱され、上方に移動するときにはキーの電流を奪います)。

バリアントA.外部PNPトランジスタを介した放電回路(Shikhmanのサイトから借用 - 「Jensenアンプ電源」を参照)。 ゲートを充電すると、ダイオードを流れる電流が外部のPNPトランジスタを閉じ、ICの出力がオフになり、ダイオードがロックされ、トランジスタが開き、ゲートをグランドに放電します。 マイナス - 小さな負荷コンデンサ(トランジスタICの電流出力によって制限される)に対してのみ機能します。

TL598(プッシュプル出力付き)を使用する場合、ビットの下側の機能はすでにチップに縫い付けられています。 この場合、オプションAは不適切です。

オプションB.独立した相補リピータ。 主電流負荷は外部のトランジスタによって処理されるので、負荷の容量(充電電流)は事実上制限されません。 トランジスタとダイオードは、飽和電圧が低く、Cと十分な電流マージン(1A以上のパルス)を持つRFです。 例えば、KT644 + 646、KT972 + 973。 リピータの「アース」は、電源スイッチのソースのすぐ隣に接続する必要があります。 トランジスタ・リピータのコレクタは、セラミック容量(図には示されていません)で陰になっていなければなりません。

どちらの回路を選択するかは、主に負荷の性質(ゲート容量またはスイッチングチャージ)、動作周波数、パルス前の時間要件に依存します。 そして、熱損失の大部分が散逸するのは、MISコアの過渡的プロセスにあるため、それらは(できる限り早く)すべきです。 私は問題の完全な分析についてはInternational Rectifierのコレクションにある出版物を参照することをお勧めします。

強力なトランジスタ(IRFI1010N)は、ゲートQg = 130nCでリファレンスが完全に充電されます。 このトランジスタは、可能な限り低いチャネル抵抗(12mOhm)を提供するために非常に大きなチャネル領域を有するため、多くのものがある。 これは12Vコンバータで必要とされるこれらのキーです。各キーはアカウントの100万個です。 チャネルの開放を保証するためには、ゲートは、全ゲート電荷Qg(Vg)= 60nClで、グランドに対してVg = + 6Vを供給されるべきである。 10Vに充電されたゲートの放電を保証するためには、Qg(Vg)= 90nCを解消する必要があります。

2.電流によるソフトウエアの実現、ソフトスタート、デューティサイクルの制限

一般に、電流センサの役割では、負荷回路の直列抵抗が要求されます。 しかし、彼はコンバータの出力で貴重なボルトとワットを盗み、負荷回路を制御するだけであり、主回路の短絡は検出できません。 解決策は、一次回路の誘導電流センサーです。

実際、センサ(カレントトランス)は小型のトロイダルコイルです(センサ巻線に加えて、その内径は主電源トランスの一次巻線を自由に通過しなければなりません)。 トロイドを通して、変圧器の一次巻線の線を通す(しかし、線源のアース線は通過しない)。 検出器の成長の時定数は、クロック周波数の3-10周期程度に設定され、フォトカプラの動作電流(1.2-1.6Vの電圧降下で約2-10mA)から10倍以上に減衰します。

図の右側には、TL494の2つの典型的なソリューションがあります。 分周器Rdt1-Rdt2は、最大デューティ・サイクル(最小の休止相)を指定します。 たとえば、Rdt1 =4.7kΩ、出力4でRdt2 =47kΩ 定電圧 Udt = 450mVであり、これは18.22%の休止相に相当する(ISシリーズおよび動作周波数に依存する)。

電源がオンになると、Cssが放電され、DT入力の電位はVref(+ 5V)になります。 CssはRss(Rdt2)を介して充電され、潜在的なDTを分周器によって境界付けられた下限までスムーズに落とします。 これは「ソフトスタート」です。 Css =47μFと示されている抵抗の場合、回路の出力はスイッチを入れてから0.1秒後に開き、さらに0.3~0.5秒間作動デューティサイクルになります。

この方式では、Rdt1、Rdt2、Cssに加えて、2つのリークがあります。オプトカプラのリーク電流(10μA以下 高温、室温で0.1〜1μAのオーダー)、入力DTから流れる入力ICトランジスタのベースの電流。 100オームよりも高くない - これらの電流が大幅に分周器の精度に影響を与えないことを、RDT2 = RSSとはせいぜい5オーム、RDT1を選択します。

もちろん、オプトカプラと制御用DT回路の選択は必須ではありません。 コンパレータモードでエラーアンプを使用することも可能であり、発電機や抵抗(例えば、同一のフォトカプラ)の能力をブロックする - それはオフではなく、滑らかな制約です。